Dokąd zmierzamy idąc krzemową doliną i poza nią? Egzotyka nieograniczonych możliwości

Nieoficjalne źródła tych doniesień podają, że sięgający nowych rubieży miniaturyzacji proces produkcyjny TSMC wykorzystuje metodę wspomaganą sztuczną inteligencją o nazwie AutoDMP, która jest zasilana przez chipy DGX H100 firmy Nvidia. Sztuczna inteligencja ma optymalizować projekty chipów trzydzieści razy szybciej niż inne techniki.

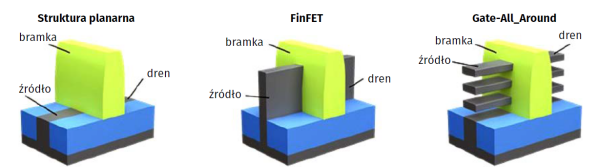

W ramach procesu 2 nm TSMC przejdzie na tranzystory GAAFET (gate-all-around), które mają zwiększyć gęstość tranzystorów i poprawić wydajność w stosunku do układów 3 nm o 10-15 procent przy tym samym poziomie mocy lub zużywać o 20–25 procent mniej energii przy tej samej wydajności. Tranzystor FET typu gate-all-around, w skrócie GAAFET, znany również jako tranzystor z bramką otaczającą (SGT), jest podobny w koncepcji do MOSFET - FinFET (o strukturze 3D zamiast planarnej), z wyjątkiem tego, że materiał bramki otacza obszar kanału ze wszystkich stron (1). W zależności od konstrukcji, tranzystory FET typu gate-all-around mogą mieć dwie lub cztery efektywne bramki. FET typu gate-all-around zostały z powodzeniem wytrawione na nanodrutach InGaAs, które mają wyższą ruchliwość elektronów niż krzem.

Tranzystor MOSFET z otaczającą bramką (GAA) został po raz pierwszy zademonstrowany w 1988 roku przez zespół badawczy firmy Toshiba, w tym Fujio Masuokę, Hiroshi Takato i Kazumasę Sunouchi. Masuoka, najbardziej znany jako wynalazca pamięci flash, później opuścił firmę Toshiba i założył Unisantis Electronics w 2004 roku, aby wraz z Uniwersytetem Tohoku badać technologię otaczającej bramki. W 2006 roku zespół koreańskich naukowców z Korea Advanced Institute of Science and Technology (KAIST) i National Nano Fab Center opracował tranzystor 3 nm, najmniejsze na świecie urządzenie nanoelektroniczne, oparte na technologii GAA FinFET. GAAFET zostały wykorzystane przez IBM do zademonstrowania technologii procesowej 5 nm.

Od 2020 r. Samsung i Intel ogłosiły plany masowej produkcji tranzystorów GAAFET (w szczególności tranzystorów MBCFET), zaś TSMC podało, że będzie nadal używać FinFET w swoim węźle 3 nm, choć pracowało już nad tranzystorami GAAFET. Intel chce wypuścić swój 2-nanometrowy węzeł w 2024 roku, a Samsung planuje rozpocząć masową produkcję 2 nm w 2025 roku. Oba układy będą wykorzystywać GAAFET i tylne zasilanie w celu zwiększenia gęstości logicznej i zmniejszenia wycieków mocy. Również japońska firma Rapidus zamierza rozpocząć masową produkcję półprzewodników 2 nm do 2027 roku. Są plany wybiegające dalej w przyszłość, Samsung zamierza osiągnąć 1,4 nm do 2027 roku, podczas gdy TSMC planuje w tej perspektywie 1 nm.

Na razie Taiwan Semiconductor Manufacturing Co. (TSMC) stara się zaspokoić popyt ze strony głównego klienta Apple na chipy 3 nm. Według analityków ankietowanych przez EE Times, problemy firmy z narzędziami i wydajnością utrudniły przejście do produkcji seryjnej. TSMC i Samsung, jego kolejny największy rywal w branży chipów, ścigają się, aby wieść prym w produkcji 3 nm dla klientów takich jak Apple i Nvidia w jej wysokowydajnych komputerach (HPC) i w smartfonach. TSMC ogłosiło niedawno, że jest liderem w produkcji 3 nm.

Ostateczny lider zdobędzie lwią część zysków w branży. Według Mehdiego Hosseiniego, starszego analityka ds. badań kapitałowych w Susquehanna International Group, na razie TSMC utrzymuje pierwsze miejsce. „TSMC pozostaje preferowanym wyborem odlewni dla wiodących węzłów, ponieważ Samsung Foundry musi jeszcze zademonstrować stabilną, wiodącą technologię procesową, podczas gdy IFS [Intel Foundry Services] jest o lata świetlne od zaoferowania konkurencyjnego rozwiązania”, pisze Hosseini w „EE Times”. Według niego, w drugiej połowie 2023 roku TSMC będzie produkować procesory Apple A17 i M3 w węźle N3 (trzy nanometry), a także procesory serwerowe oparte na ASIC w węzłach N4 i N3. TSMC będzie również produkować chipy graficzne Intel Meteor Lake w N5, procesory AMD Genoa i Nvidia Grace w N5 i N4, a także GPU Nvidia H100 w N5. Brett Simpson, analityk w Arete Research, w raporcie „EE Times” dodaje: „Obecnie uważamy, że wydajność N3 w TSMC dla procesorów A17 i M3 wynosi około 55 proc. a TSMC wydaje się zgodnie z harmonogramem zwiększać wydajność o około 5+ punktów co kwartał”.

Przezwyciężyć CMOS

Technika obliczeniowa oparta na półprzewodnikach mają historię sięgającą lat 50. ubiegłego wieku, kiedy tranzystory zaczęły zastępować lampy próżniowe w układach elektronicznych. Generacje nowych urządzeń półprzewodnikowych pojawiały się i znikały. Tranzystory germanowe zostały zastąpione krzemowymi, a następnie układami scalonymi, a potem coraz bardziej złożonymi chipami wypełnionymi coraz większą liczbą mniejszych tranzystorów. Od lat sześćdziesiątych branża mierzy swoje postępy prawem Moore’a, czyli prognozami Gordona Moore’a, współzałożyciela Intela, że coraz mniejsze urządzenia będą prowadzić do stałej poprawy wydajności obliczeniowej i efektywności energetycznej.

Postępy w nanotechnologii pozwoliły na zmniejszenie najmniejszych elementów najbardziej zaawansowanych obecnie układów scalonych do skali atomowej, Kolejny ważny krok w dziedzinie obliczeń wymaga nie tylko nowych nanomateriałów, ale także nowej architektury. Tranzystory CMOS (complementary metal-oxide-semiconductor) były standardowym budulcem układów scalonych od lat 80. ubiegłego wieku. Opierają się na architekturze, którą John von Neumann wybrał w połowie XX wieku. Ta została zaprojektowana tak, by oddzielać elektronikę przechowującą dane w komputerach od elektroniki przetwarzającej informacje cyfrowe. Oddzielenie przechowywanej pamięci od procesora zapobiegała wzajemnemu zakłócaniu się sygnałów i zachowywała dokładność potrzebną do obliczeń cyfrowych. Jednak przenoszenie danych z pamięci do procesorów stało się wąskim gardłem. Deweloperzy poszukują obecnie rozwiązań alternatywnych dla architektury von Neumanna. Dążą do wykonywania obliczeń „w pamięci”, aby uniknąć marnowania czasu i energii na przenoszenie danych.

Pierwsze oznaki poważnych zmian w pojawiły się około 2012 roku, gdy postęp wynikający z prawa Moore’a zaczął słabnąć, a twórcy deep learning zdali sobie sprawę, że jednostki centralne (CPU) ogólnego przeznaczenia stosowane w konwencjonalnych komputerach nie są w stanie zaspokoić ich potrzeb. Siłą procesorów była ich wszechstronność, ale z punktu widzenia głębokiej nauki maszynowej to niekoniecznie atut. Poszukując lepszych procesorów do głębokiego uczenia, programiści IBM zwrócili się w stronę procesorów graficznych (GPU), zaprojektowanych do wykonywania zaawansowanej matematyki wykorzystywanej do szybkiego, trójwymiarowego obrazowania w grach komputerowych. Odkryto, że procesory graficzne mogą uruchamiać algorytmy głębokiego uczenia się znacznie wydajniej niż procesory centralne. W maszynach opartych na przepływie danych pewne instrukcje są wbudowane w procesor, więc nie trzeba ich ładować. W przypadku algorytmu głębokiej nauki maszynowej, około 80 proc. operacji wykorzystuje te same zaawansowane obliczenia, co przetwarzanie obrazu.

Procesory graficzne, które „już tu były” przydały się bardzo. Nie oznacza to, że wszyscy traktują je jako rozwiązanie ostateczne. Istnieje wiele nowych pomysłów, nowych urządzeń i nowych nanostruktur, ale wciąż nie wydają się gotowe do zastąpienia CMOS, i kart graficznych, ma się rozumieć.

Próby odtwarzania neuronów mózgu

Jednym z kierunków poszukiwań są systemy neuromorficzne, które wykorzystują algorytmy i projekty sieci, naśladujące wysoką łączliwość i równoległe przetwarzanie ludzkiego mózgu. Wymaga to opracowania nowych typów sztucznych neuronów i synaps, które są kompatybilne z przetwarzaniem elektronicznym, ale przewyższają wydajność obwodów CMOS.

Jednym z najpopularniejszych pomysłów na układy neuromorficzne są memrystory. Przypominają standardowe rezystory elektryczne, ale z elektryczną regulacją oporu, co w tym przypadku oznacza zarazem modyfikację danych przechowywanych w pamięci. Dzięki trzem warstwom - dwóm terminalom, które łączą się z innymi urządzeniami, oddzielonym warstwą pamięci - ich struktura pozwala na przechowywanie danych i przetwarzanie informacji. Koncepcja ta została zaproponowana w 1971 roku, ale dopiero w 2007 roku R. Stanley Williams z laboratoriów Hewletta-Packarda w Kalifornii, stworzył pierwszy cienkowarstwowy memrystor półprzewodnikowy, który można było wykorzystać w obwodzie.

Naukowcy poszukują nowych klas materiałów, aby zaspokoić potrzeby zaawansowanych obliczeń. Mark Hersam i Vinod K. Sangwan, materiałoznawcy z Uniwersytetu Northwestern, skatalogowali niedawno obszerną listę potencjalnych neuromorficznych materiałów elektronicznych, która obejmuje materiały „zerowymiarowe” (kropki kwantowe), materiały jedno- i dwuwymiarowe (np. grafen) oraz heterostruktury van der Waalsa (wiele dwuwymiarowych warstw materiałów, które przylegają do siebie). Sporo uwagi jako potencjalne materiały do zastosowania w systemach neuromorficznych przyciągnęły nanorurki węglowe, ponieważ fizycznie przypominają rurkowate aksony, przez które komórki nerwowe przesyłają sygnały elektryczne w systemach biologicznych. Jednak, zdania co do tego, jak materiały te wpłyną na przyszłość informatyki, są podzielone.

Kwanty i egzotyka

Omawiając futurystyczne perspektywy elektroniki, nie sposób pominąć poszukiwań związanych z innym nurtem świata obliczeń przyszłości - komputerami kwantowymi. Tu też się poszukuje i to w nieco podobnych do systemów neuromorficznych obszarach, np. w świecie kropek kwantowych wykonanych z dwuwarstwowego grafenu. Badania nad nimi zostały przeprowadzone m.in. przez Christopha Stampfera z Uniwersytetu RWTH w Akwizgramie. Jego zespół zademonstrował, że struktura ta może pomieścić elektron w jednej warstwie i dziurę w drugiej. Co więcej, kwantowe stany spinowe tych dwóch jednostek są niemal idealnymi swoimi lustrzanymi odbiciami.

Kropka kwantowa to niewielki kawałek półprzewodnika o właściwościach elektronicznych, które bardziej przypominają atom niż materiał objętościowy. Na przykład, elektron w kropce kwantowej jest wzbudzany do skwantowanych poziomów energetycznych, podobnie jak w atomie. To przypominające atom zachowanie można precyzyjnie dostroić, dostosowując rozmiar i kształt kropki kwantowej. Kropka kwantowa może być wykonana z małych kawałków grafenu, arkusza węgla o grubości zaledwie jednego atomu. Takie kropki kwantowe mogą być wykonane tylko z jednego arkusza grafenu, dwóch arkuszy (grafen dwuwarstwowy) lub więcej (2).

Jednym z obiecujących zastosowań grafenowych kropek kwantowych jest tworzenie bitów kwantowych (kubitów), które przechowują informacje w stanach spinowych elektronów. Dziury, jak wiadomo z fizyki tranzystorów, powstają w półprzewodnikach, gdy elektron jest wzbudzony. Dwuwarstwowy grafen może uwięzić elektrony i dziury po przyłożeniu do nich zewnętrznego napięcia - tworząc strukturę bramki. W 2018 r. udało się po raz pierwszy osiągnąć w takim układzie w dwuwarstwowym grafenie przerwę pasmową indukowaną przez pole elektryczne. Była to duża rzecz, gdyż wcześniej grafen zawodził swoich entuzjastów w dziedzinie elektroniki właśnie dlatego, że nie oferował pasma zabronionego, tak jak półprzewodniki. Osiągnięcie to pozwalało na transport przez tworzenie i anihilację pojedynczych par elektron-dziura o przeciwnych liczbach kwantowych, Zdaniem uczonych, powinno być możliwe łączenie kubitów elektronowo-spinowych na większe odległości, przy jednoczesnym bardziej niezawodnym odczytywaniu ich spinowo symetrycznych stanów. Dzięki temu komputery kwantowe mogłyby zyskać na skali i bezbłędności.

Poszukiwania nowej elektroniki kierują się coraz bardziej egzotyczne obszary fizyki - w tym wydaniu MT piszemy w Infozoomie o postępach firmy Microsoft, która buduje kwantowe układy obliczeniowe oparte na tzw. fermionach Majorany. A to nie koniec egzotyki w badaniach nad nową elektroniką. Według niedawnej publikacji w „Advanced Materials”, Korea Research Institute of Standards and Science (KRISS) opracował niedawno pierwszy na świecie tranzystor zdolny do kontrolowania skyrmionów, kwazicząstek będących formacjami pola magnetycznego. Można je zminiaturyzować do kilku nanometrów, dzięki czemu są ruchome przy wyjątkowo niskiej mocy. Ta cecha czyni je kluczowym elementem w rozwoju spintroniki. Zespół KRISS opracował metodę jednolitej kontroli anizotropii magnetycznej przez wykorzystanie wodoru w izolatorach z tlenku glinu. Opracowanie tranzystora spintronicznego ma przyspieszyć rozwój m.in. urządzeń neuromorficznych i bramek logicznych, przy znacznych korzyści w zużyciu energii, stabilności i szybkości w porównaniu z tradycyjnymi urządzeniami elektronicznymi.

Z drugiej strony dla elektroniki mniej wymagającej szuka się rozwiązań może nie z obszarów fizyki egzotycznych cząstek, ale wciąż wykorzystującej dość egzotyczne pomysły i materiały, takie jak… drewno. W ostatnim czasie naukowcy z uniwersytetów szwedzkich Linköping i KTH stworzyli pierwszy na świecie drewniany tranzystor. Twarde drewno balsa pozbawili ligniny i wypełnili mieszaniną polimerów przewodzących o nazwie poli (3,4-etylenodioksytiofen) -polistyrenosulfonian lub PEDOT:PSS. Układając jednostki o grubości milimetra, które działały jako elektrody i kanały, zespół odkrył, że powstaje w ten sposób rodzaj tranzystora. Po podaniu napięcia 6 V, kanał wypełnia się elektronami, stopniowo zamykając się i przełączając przełącznik w pozycję „wyłączony”. Wyłączenie drewnianego urządzenia zajmuje około sekundy, podczas gdy przywrócenie go do pozycji włączonej zajmuje około pięciu sekund. Biodegradowalna elektronika mogłaby, zdaniem uczonych, być wykorzystywana w zdalnych czujnikach, które muszą się łatwo zepsuć lub niepozornych urządzeniach zasilanych w środowisku.

Mirosław Usidus